# **Novelics coolREG™**

DATASHEET

coolREG memory IPs provide solutions for synchronous single-port, dual-port, and two-port register files requirements. The coolREG IP is based on the production-proven, foundry-provided 6T SRAM (single-port) or 8T SRAM (dual-or two-port) cell and offers advanced leakage control features and near-zero setup times. These dense memories let the designer specify the number of bits in each word and select the aspect ratio for each specific register file to meet the application's need.

Novelics patented circuit technologies minimizes leakage current and active power in both the memory core and the peripheral circuits. In addition, the coolREG has been optimized to meet the performance requirements of very high speed applications such as processor cache.

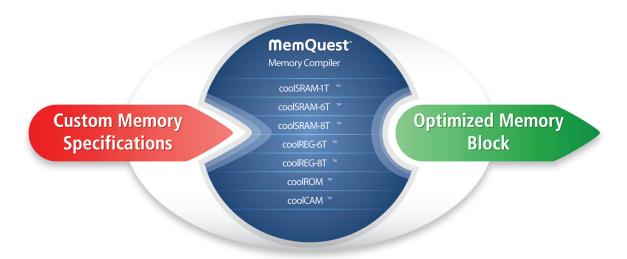

The coolREG IP has been thoroughly simulated and validated in silicon to ensure the highest level of manufacturability. The MemQuest™ memory compiler has been verified and characterized to ensure the highest quality of deliverables.

Novelics coolREG™ embedded memory IPs are ideal solutions for System-on-Chip (SoC), ASIC, and ASSP applications requiring low-power, high-speed, and high-density configurable register files. Embedded coolREG delivers the best performance and power characteristics for small and fast Register File instances.

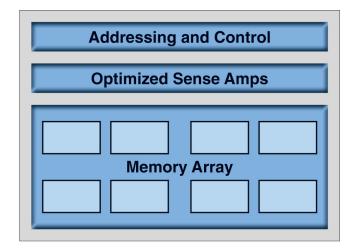

coolREG general architecture

#### **FEATURES:**

- Customer architected through the MemQuest memory compiler and characterization tool

- Reliable, silicon-proven architecture

- Single-port, dual-port, and twoport architectures

- Based on foundry-provided 6T SRAM (single port) or 8T SRAM (dual port and two-port) cell

- Support for single and dual clock domains

- In the two-port register file, the read and write ports are completely independent and can read any location simultaneously

- The dual-port clocked register file provides two read and write ports that share the same memory space. Each port can operate in independent clock domains.

- Reliable operation and performance well beyond normal Process/Voltage/Temperature (PVT) variations

- Support for SVT & HVT Transistors

- User definable word width, depth and aspect ratio

- Memory options to meet power, speed, and area design criteria

- Easily configurable options including subword writeable

- Optimized for high performance and low-power designs

- Design utilizes up to 4 layers of metal

- Flexible routing over macro in metal 5 and above

- Supports power mesh

- Minimal setup time

### **MemQuest Memory Compiler Top Level Flow**

| Selection                   | Area<br>(mm²) ⊡ | X<br>(mm) | Y<br>(mm) | Access Time (ns) | Power<br>(mW) | Active Leakage (mA) | Sleep Leakage<br>(mA) |

|-----------------------------|-----------------|-----------|-----------|------------------|---------------|---------------------|-----------------------|

| Operating Conditions (PVT): |                 |           |           | wc * <b>▼</b>    | tc ▼          | tc ▼                | tc 🔻                  |

| 1 0                         | 0.822           | 1.29      | 0.635     | 1.4              | 0.003         | 0.337               | 0.0002                |

| 2 0                         | 0.855           | 2.46      | 0.347     | 1.5              | 0.0045        | 0.341               | 0.0003                |

| 3 0                         | 0.860           | 0.710     | 1.21      | 1.59             | 0.0024        | 0.341               | 0.0003                |

| 4 ⊙                         | 0.889           | 1.29      | 0.687     | 1.18             | 0.0025        | 0.343               | 0.0003                |

| 5 0                         | 0.919           | 2.46      | 0.373     | 1.27             | 0.0033        | 0.344               | 0.0003                |

| 6 0                         | 0.933           | 0.710     | 1.31      | 1.39             | 0.0022        | 0.353               | 0.0004                |

| 7 🔘                         | 1.02            | 1.29      | 0.790     | 1.08             | 0.0024        | 0.357               | 0.0004                |

| 8 0                         | 1.04            | 0.440     | 2.36      | 2.41             | 0.0031        | 0.355               | 0.0004                |

| 9 🔿                         | 1.05            | 2.46      | 0.424     | 1.16             | 0.0029        | 0.352               | 0.0004                |

| 10 🔿                        | 1.30            | 2.46      | 0.527     | 1.11             | 0.003         | 0.366               | 0.0005                |

## Typical MemQuest Memory Compiler for Architectural Trade off Analysis

#### For the latest product information, call us or visit: www.mentor.com

©2011 Mentor Graphics Corporation, all rights reserved. This document contains information that is proprietary to Mentor Graphics Corporation and may be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies. In accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. All trademarks mentioned in this document are the trademarks of their respective owners.

**Corporate Headquarters Mentor Graphics Corporation** 8005 SW Boeckman Road Wilsonville, OR 97070-7777 Phone: 503.685.7000 Fax: 503.685.1204

Sales and Product Information Phone: 800.547.3000 sales\_info@mentor.com

Silicon Valley **Mentor Graphics Corporation** 46871 Bayside Parkway Fremont, CA 94538 USA Phone: 510.354.7400 Fax: 510.354.7467

North American Support Center Phone: 800.547.4303

Europe Mentor Graphics **Deutschland GmbH** Arnulfstrasse 201 80634 Munich Germany Phone: +49.89.57096.0

Fax: +49.89.57096.400

Pacific Rim Mentor Graphics (Taiwan) Room 1001, 10F International Trade Building No. 333, Section 1, Keelung Road Taipei, Taiwan, ROC

Phone: 886.2.87252000 Fax: 886.2.27576027

Japan Mentor Graphics Japan Co., Ltd.

Gotenyama Garden 7-35, Kita-Shinagawa 4-chome Shinagawa-Ku, Tokyo 140-0001 Japan

Phone: +81.3.5488.3033 Fax: +81.3.5488.3004

<sup>\*</sup> Note the instance that is most optimal in each column is highlighted in green.