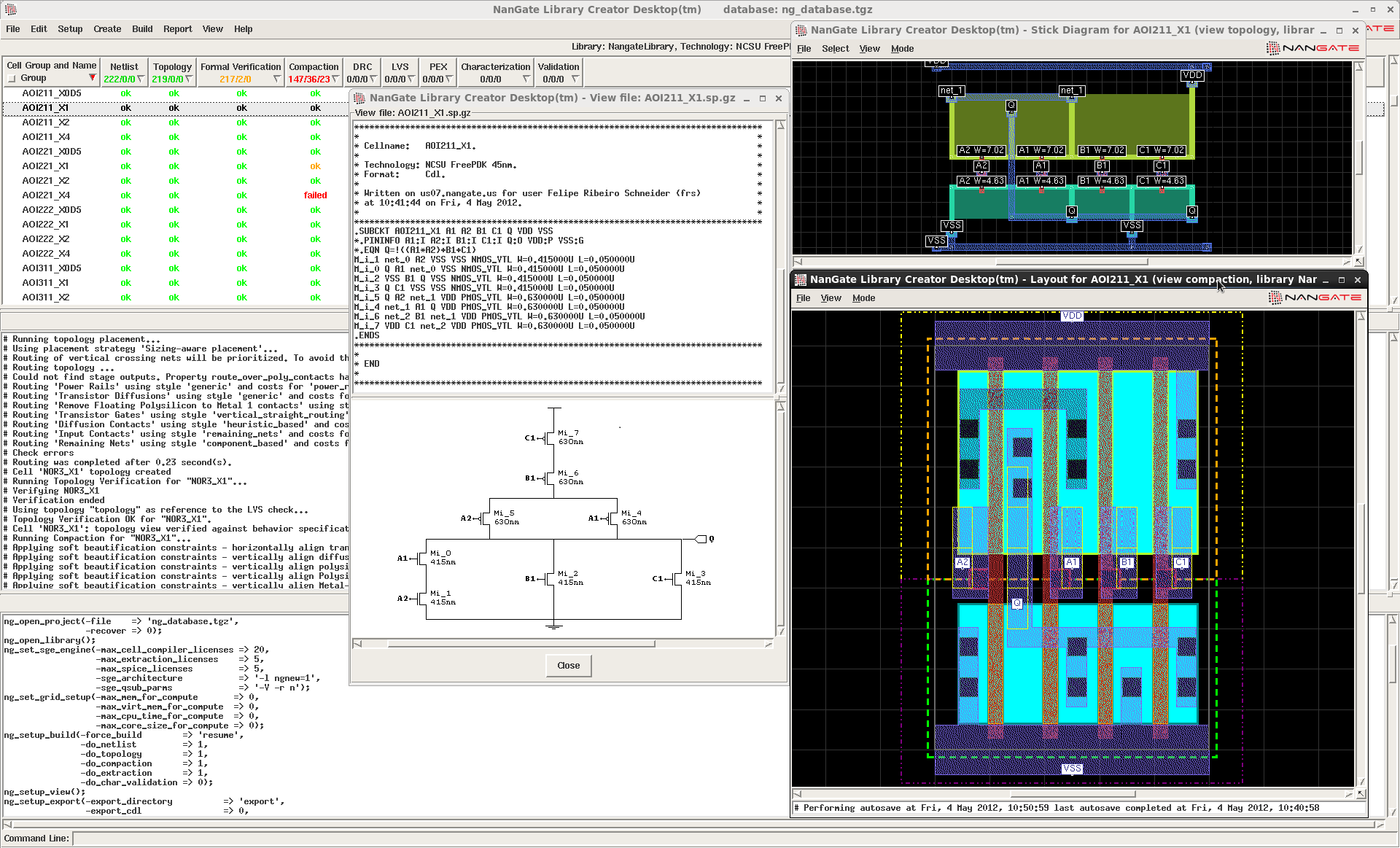

NanGate Library Creator™ is the industry’s most versatile, integrated and easy-to-use solution for digital cell library creation and optimization. It enables designers of digital CMOS ICs to custom-tailor digital cell libraries and explore the impact of alternate device models, design rules and cell architectures, as well as process migration.

With NanGate Library Creator, designers can control and alter the individual attributes of all digital library cells, making precise adjustments to cell parameters to fulfill the strictest design requirements.

For example, transistor sizing strategy and row height can be set to control the trade-off between power usage, frequency and area. Drive strength variants, which can be any arbitrary number, can be set at will and the user can balance DFM trade-offs between recommended and required rules, thus optimizing layout resolution without an increase in the total cell area.

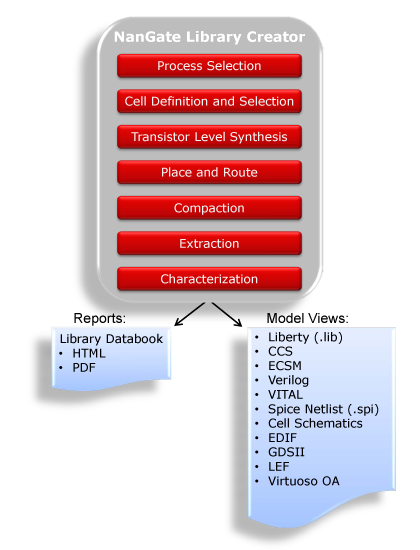

NanGate Library Creator contains the full set of tools needed to create and characterize standard cell libraries. It complements existing design flows and provides all of the outputs required by the physical synthesis tool chain.

Key Features and Benefits:

-

Intelligent library planner allows fast and easy design space exploration with minimal data entry, this enables users to define and create the optimal library for the application in a minimum of time

-

Fast setup and assimilation of process technologies and foundry design rules, enabling DRC clean layout generation in the first week of use

-

Advanced routing engine, capable of routing standard cells while taking all complex rules and routing restrictions into consideration, hereby maximizing resource utilization in 28nm process node and below

-

Advanced process technology support down to 22nm, including context sensitive spacing and enclosure rules, tip-to-tip and tip-to-side minimization, preferred shape patterns, double-patterning and support of local interconnect

-

Discreet transistor-sizing for FinFET and other non-planar technologies

-

Scalable parallel processing, so that run times scale linearly with the number of compute nodes and parallel simulations

-

Built-in SPICE simulator (Nanspice™) with optional integration with third-party SPICE simulators and extraction engines

-

Integration with leading third-party DFM, DRC and LVS verification tools to ensure high-quality sign-off layouts and minimal disruption to customer existing flows

-

Generate footprint-compatible cells starting with GDSII or automatically generated layouts to create fine-grained drive and skew variants, enabling late-stage speed and power optimization using NanGate Design Optimizer™

-

Advanced Layout Migration Flow

- Significant productivity improvement

- Migrates entire cell libraries to different process technologies or cell architectures

-

Uses cell templates to configure predefined shapes, routing parameters, track height, gate pitch, P/N ratios, size and position of power rails, etc.

-

Resizes transistors to satisfy new template or drive strength requirements, also allowing creation of gate length variants required for low leakage applications

-

Supports wide range of layout migration methodologies including equation-based input to GDS-based layout migration, depending on how much the layout must be stripped from its characteristics, supporting a broad range of applications

-

Full scripting interface support provides the flexibility to integrate NanGate Library Creator into existing design flows and perform design goal searching through iterative loops

General Features:

Fully automated layout topology generation using advanced optimization algorithms that minimize cell area and parasitic effects. Optimization strategies include:

-

Optimal cell input sequencing

-

Optimal diffusion strip layout

-

Transistor netlist synthesis with built-in transistor sizing algorithms and override options including logical effort

-

Adaptive or user-enforced application of recommended rules and wire-spreading for DFM improvement

-

User-definable topology generators with support for an advanced parameterized set of layout primitives:

- Contact and contact arrays

- Single and folded transistor configurations

- Routing preferences and pattern restrictions/allowances

- Input and output port guidance and blockages

-

Advanced proprietary compaction engine:

- Adaptive topology-driven compaction strategies

- Full design-rule support for advanced CMOS processes as well as user constraints

-

Scalable parallel execution of SPICE simulations and layout generation through:

- LSF™ from Platform Computing®

- SUN® Grid Engine (SGE)

- Multi- and single-threaded processing

-

Built-in verification, including:

- Formal verification of layout vs. expression

- Extensive timing and power model validation

- Interface to external physical verification for independent QA

- DFM analysis and scoring through external verification tools

Cell Types

- Buffers (inverting, non-inverting, clock)

- Boolean combinational (AND, OR, NAND, NOR, AOI, OAI, OA, AO, MUX)

- Arithmetic (XOR, full-adder, half-adder)

- Sequential (latches, clock-gates, D-type flip/flops with any optional combination of scan input, set and reset)

- Miscellaneous (tie cells, filler cells, antenna, diode, ECO gates)

- User-defined complex gates based on Boolean equations

- User-defined cells from SPICE netlists

Inputs

- Foundry provided transistor models

- NanGate Technology Language file containing foundry design rules

Outputs

- Liberty (.lib) formatted libraries with CCS, ECSM and NLDM/NLPM data

- Verilog® and SPICE netlists

- LEF (Library Exchange Format)

- GDSII (Graphics Design System II) cell layouts

- Library databook in HTML and PDF format

- Cell schematics

- Open Access database

- VITAL

Platform Support

- Redhat Linux® x86 and x86_64

|

|

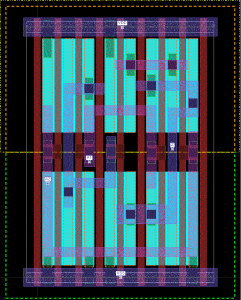

XOR2 cell sample (FreePDK15) |

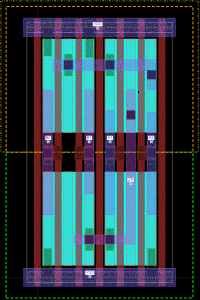

AOI22 cell sample (FreePDK15) |

|